86-0755-27838351

频率:14.31818-166MHZ

尺寸:5.0*3.2mm

京瓷晶振,有源晶振,KC5032E-C3晶振,有源晶振,是只晶体本身起振需要外部电压供应,起振后可直接驱动CMOS 集成电路,产品本身已实现与薄型IC(TSSOP封装,TVSOP封装)同样的1mm厚度,断开时的消费电流是15 µA以下,编带包装方式可对应自动搭载及IR回流焊接(无铅对应)产品有几种电压供选1.8V,2.5V,3V3.3V,5V,以应对不同IC产品需要

恒温晶振的真空封装技术:是指石英晶振在真空封装区域内进行封装。1.防止外界气体进入组件体内受到污染和增加应力的产生;2.使晶振组件在真空下电阻减小;3.气密性高。此技术为研发及生产超小型、超薄型石英晶振必须攻克的关键技术之一

|

项目 |

符号 |

规格说明 |

条件 |

|

输出频率范围 |

f0 |

14.31818-166MHz |

请联系我们以便获取其它可用频率的相关信息 |

|

电源电压 |

VCC |

2.97-3.63 V |

请联系我们以了解更多相关信息 |

|

储存温度 |

T_stg |

-55℃ to +125℃ |

裸存 |

|

工作温度 |

T_use |

-10℃ to +70℃ |

请联系我们查看更多资料http://www.crystal95.com |

|

|

|||

|

|

|||

|

频率稳定度 |

f_tol |

J: ±50 × 10-6 |

|

|

L: ±100 × 10-6 |

|||

|

T: ±150 × 10-6 |

|||

|

功耗 |

ICC |

3.5 mA Max. |

无负载条件、最大工作频率 |

|

待机电流 |

I_std |

3.3μA Max. |

ST=GND |

|

占空比 |

SYM |

45 % to 55 % |

50 % VCC 极, L_CMOS≦15 pF |

|

输出电压 |

VOH |

VCC-0.4V Min. |

|

|

VOL |

0.4 V Max. |

|

|

|

输出负载条件 |

L_CMOS |

15 pF Max. |

|

|

输入电压 |

VIH |

80% VCC Max. |

ST 终端 |

|

VIL |

20 % VCC Max. |

||

|

上升/下降时间 |

tr / tf |

4 ns Max. |

20 % VCC to 80 % VCC 极, L_CMOS=15 pF |

|

振荡启动时间 |

t_str |

3 ms Max. |

t=0 at 90 % |

|

频率老化 |

f_aging |

±3 × 10-6 / year Max. |

+25 ℃, 初年度,第一年 |

石英晶振自动安装和真空化引发的冲击会破坏产品特性并影响这些产品。请设置安装条件以尽可能将冲击降至最低,5032晶体振荡器并确保在安装前未对晶振特性产生影响。条件改变时,请重新检查安装条件。同时,在安装前后,请确保石英晶振产品未撞击机器或其他电路板等。

每个封装类型的注意事项

(1)陶瓷包装晶振与SON产品

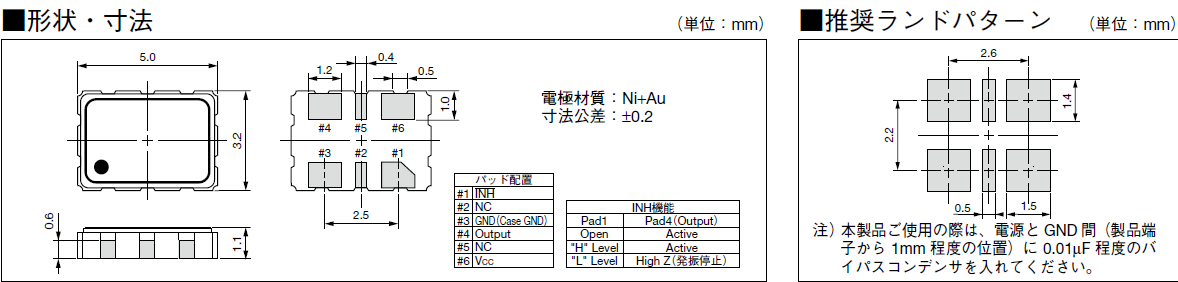

在焊接陶瓷封装晶振和SON产品 (陶瓷包装是指晶振外观采用陶瓷制品) 之后,弯曲电路板会因机械应力而导致焊接部分剥落或封装分裂(开裂)。6脚有源振荡器尤其在焊接这些产品之后进行电路板切割时,务必确保在应力较小的位置布局晶体并采用应力更小的切割方法。

(2)陶瓷包装石英晶振

在一个不同扩张系数电路板(环氧玻璃)上焊接陶瓷封装石英晶振时,在温度长时间重复变化时可能导致端子焊接部分发生断裂,请事先检查焊接特性。

(3)柱面式产品

产品的玻璃部分直接弯曲引脚或用力拉伸引脚会导致在引脚根部发生密封玻璃分裂(开裂),也可能导致气密性和产品特性受到破坏。5032晶体振荡器当有源晶振的引脚需弯曲成下图所示形状时,应在这种场景下留出0.5mm的引脚并将其托住,以免发生分裂。当该引脚需修复时,请勿拉伸,托住弯曲部分进行修正。在该密封部分上施加一定压力,会导致气密性受到损坏。所以在此处请不要施加压力。另外,为避负机器共振造成引脚疲劳切断,建议用粘着剂将产品固在定电路板上。

京瓷晶振,有源晶振,KC5032E-C3晶振

电话:+86-0755-278383514

手机:138-2330-0879

QQ:632862232

地址:广东深圳市宝安宝安大道东95号浙商银行大厦1905